- sales/support

Google Chat:---

- sales

+86-0755-88291180

- sales01

sales@spotpear.com

- sales02

dragon_manager@163.com

- support

tech-support@spotpear.com

- CEO-Complaints

zhoujie@spotpear.com

- Only Tech-Support

WhatsApp:13246739196

- Purchase/Shipping/Refund

WhatsApp:13424403025

- HOME

- >

- ARTICLES

- >

- Milk-V

- >

- Milk-V Duo

Milk-V Duo S SG2000 Public Preliminary Datasheet

Introduction of SG2000

SG2000 is a high-performance, low-power chip designed for various product fields such as edge intelligent surveillance IP cameras, local facial recognition attendance machines, and smart home devices. It integrates H.264/H.265 video compression and decoding and ISP capabilities. It supports various image enhancement and correction algorithms like HDR wide dynamic range, 3D noise reduction, defogging, and lens distortion correction, providing customers with professional-grade video image quality.

The chip also integrates an in-house TPU, delivering approximately 0.5TOPS of computing power under INT8 operations. The specially designed TPU scheduling engine efficiently provides high-bandwidth data flow for tensor processing unit cores. It also offers users a powerful deep learning model compiler and software SDK development kit. Mainstream deep learning frameworks such as Caffe, Pytorch, ONNX, MXNet, and TensorFlow (Lite) can be easily ported to this platform.

【SG2000 Public Preliminary Datasheet】

We have open sourced the Public Preliminary Datasheet and TRM of SG2000 to GitHub. please check it out.

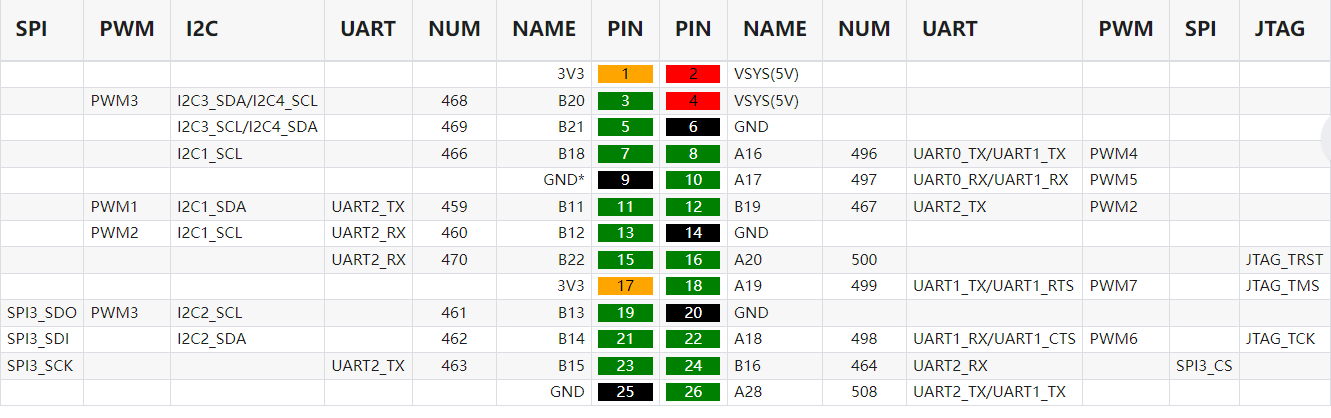

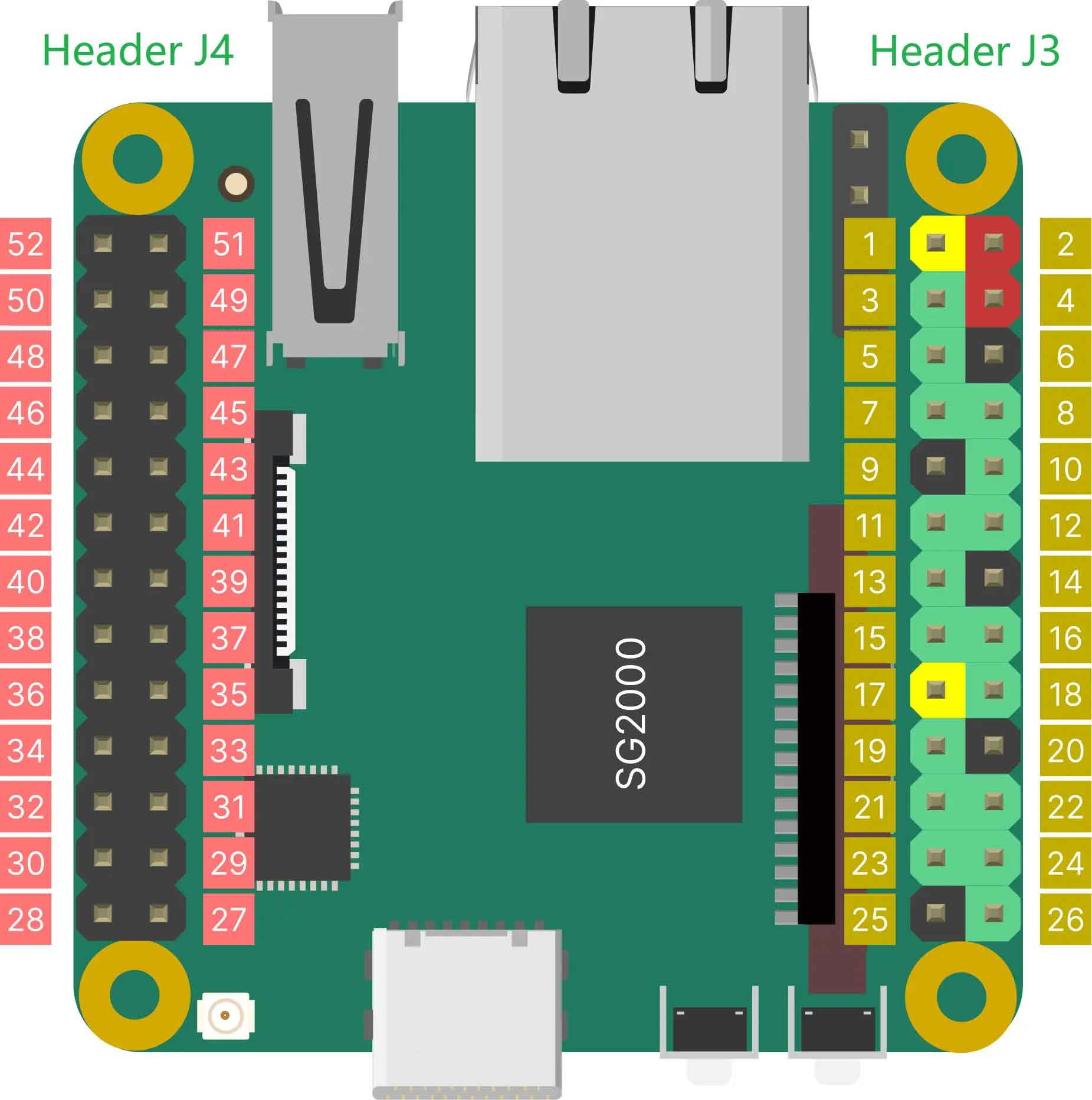

DuoS GPIO Pinout

GPIO pin mapping

|

|---|

Header J3

GPIO oPIO on Header J3 use 3.3V logic levels.

|

|---|

GND*: Pin 9 is a low-level GPIO in the V1.1 version of the hardware, and is GND in the V1.2 version and later.

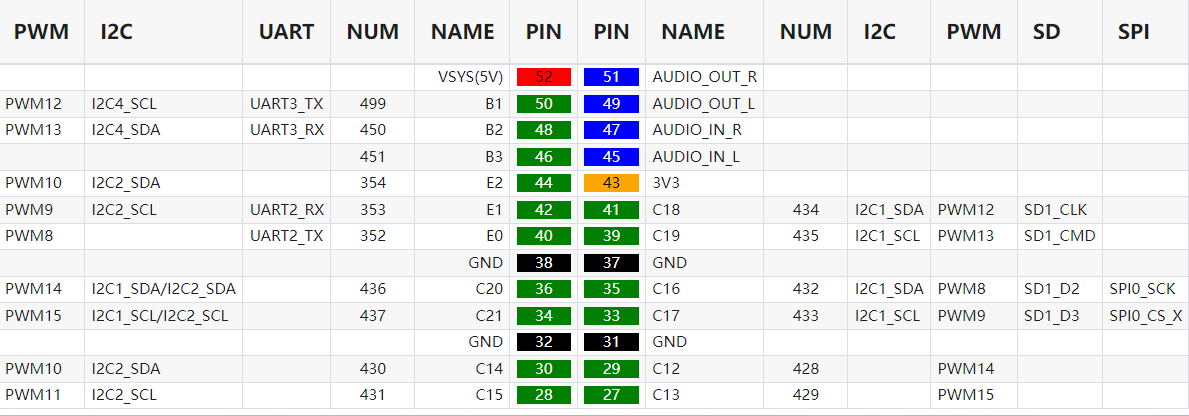

Header J4

GPIO E0/E1/E2 on Header J4 use 1.8V logic levels.

|

|---|

LED PIN

| NAME | SG2000 | NUM |

|---|---|---|

LED | XGPIOA[29] | 509 |

TAG:

Raspberry Pi 5 PCIe to M.2 Mini NVMe SSD Board (E) With Customized Active Cooler Together

ESP32-S3 Development Board 4 inch LCD TouchScreen Display 480x480 RS485 /SHT20 /Relay For Arduino LVGL 86 TVbox

MAX9296 GMSL Camera Adapter Board 2-Ch High-Speed And Low-Latency Transmission For Jetson Orin Nano/NX

Raspberry Pi 5 Case

0.96inch1.3inch1.44inch1.8inch LCD Display Screen Round Arduino Raspberry Pi ESP32 Pico STM32

7.5 inch Passive NFC e-Paper BW Display 7.5inch E-ink Screen No Need Battery Wireless Powered Data Transfer

DAPLINK

Raspberry Pi Pico 2 RP2350 With 0.96 inch LCD Display 0.96inch Screen 160×80 Onboard RP2350A

Template: Pico-get-start

Raspberry Pi Pico 2 RP2350B 4.3inch Capacitive TouchScreen 4.3 inch LCD Display Development Board 800×480

Jetson Nano Heatsink

Raspberry Pi 8inch LCD 768x1024 Capacitive TouchScreen HDMI Display

Raspberry Pi 5 PD Induction

Raspberry Pi Compute Module 5 CM5 Cortex A76 BCM2712 With/Without Wi-Fi RAM 2/4/8/16GB eMMC Lite/8/16/32/64GB

Gripper Serial Robotic Arm Gripper Mechanical claw Serial Bus Servo ST3215/CF35-12

Milk-V Duo HUB

ESP32-S3 GEEK

Raspberry Pi USB Camera 2MP OV2735 Distortion-Free USB 2.0 For Jeston RDK

Raspberry Pi Pico 2 RP2350 3.5 inch LCD Capacitive 3.5inch TouchScreen Development Board 240x320 Display QMI8658 6-Axis /OV5640 Camera /SD

X1006 Raspberry Pi 5 PCIe To 2.5 SATA And M.2 KEY-B 2280 SSD/HDD Double-SATA (NOT BOOT From SATA/SSD

TAG:

Raspberry Pi LCD

Raspberry Pi DSI display

Raspberry Pi Compute Module 5 CM5 IO Board

Robotic Arm Gripper Mechanical claw Servo ST3215 CF35-12

D-Robotics RDK X3 Module

Raspberry Pi 5 POE PD Trigger Activation Type C Power Over Ethernet 802.3af/at Pi5

Raspberry Pi 5 MIPI Camera Cable

ESP32-S3 Smart 86 Box Development Board with 4 inch 480x480 Display Touch Screen For AI and DeepSeek

LuckFox Pico SC3336

DeepSeek AI Voice Chat ESP32 S3 Development Board 1.8 inch AMOLED Display 368×448 1.8inch TouchScreen Programmable Watch

Type-C Power Adapter

RISC V

ESP32 AI Voice Chat Robot 1.54inch Development Board with 1.54 inch LCD Display Screen Deepseek

USB To CAN FD Bus Data Analyzer Bus Communication

Sipeed NanoKVM-USB

Raspberry Pi 5 Original FFC Cable

MAX9296 GMSL Camera 2-Ch High-Speed Low-Latency Transmission Jetson Orin Nano/NX

ISX031 GMSL Camera H100 H190 Image Sensor IP67 protection rating For Jetson Orin And MAX96717 GMSL camera

DeepSeek ESP32-S3 Voice Chat Robot

ADXL354CEZ