- sales/support

Google Chat:---

- sales

+86-0755-88291180

- sales01

sales@spotpear.com

- sales02

dragon_manager@163.com

- support

tech-support@spotpear.com

- CEO-Complaints

zhoujie@spotpear.com

- Only Tech-Support

WhatsApp:13246739196

- Purchase/Shipping/Refund

WhatsApp:13424403025

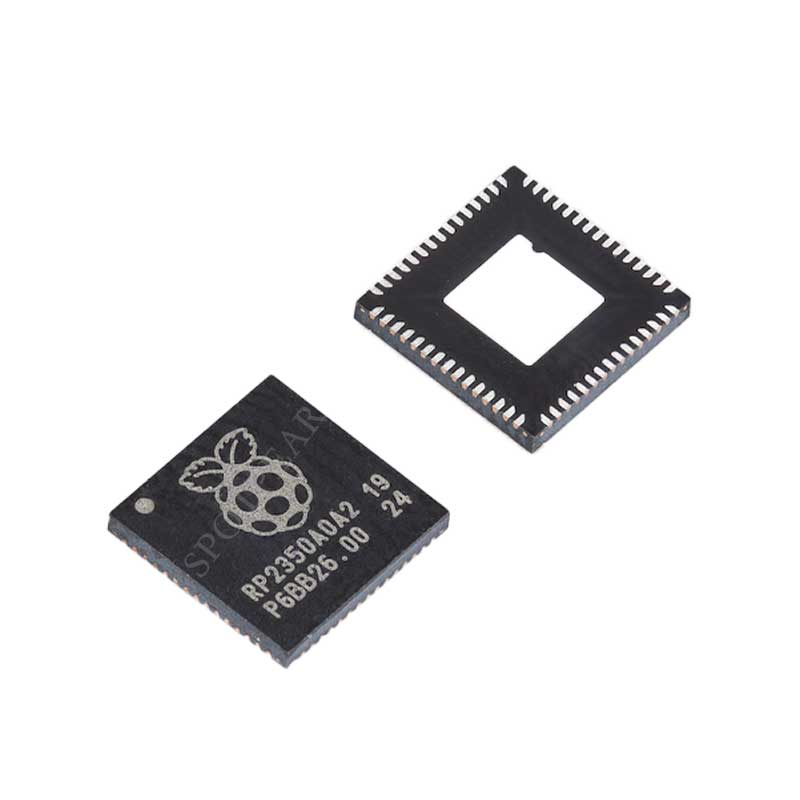

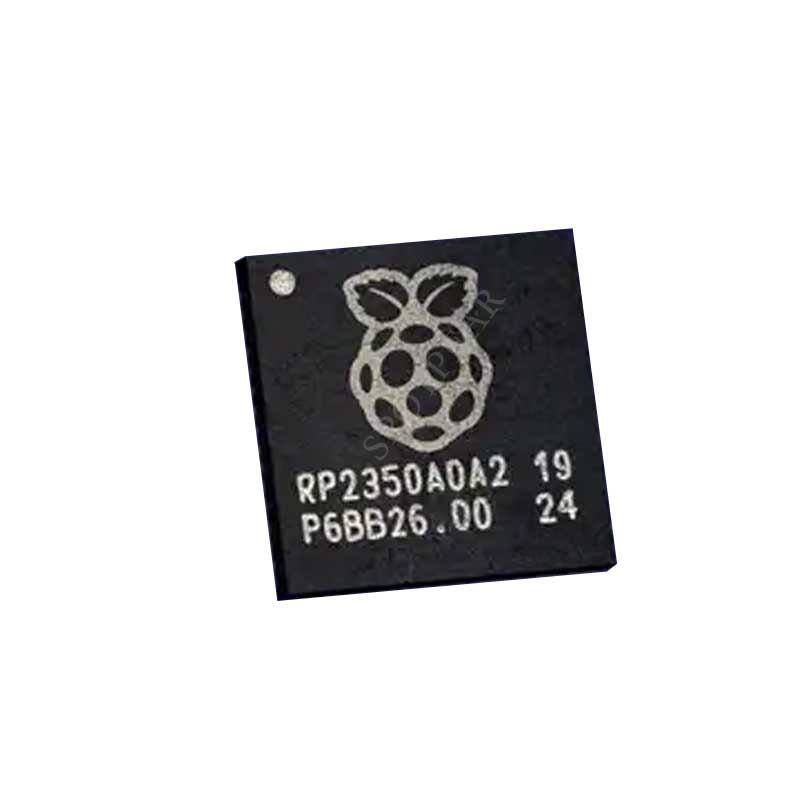

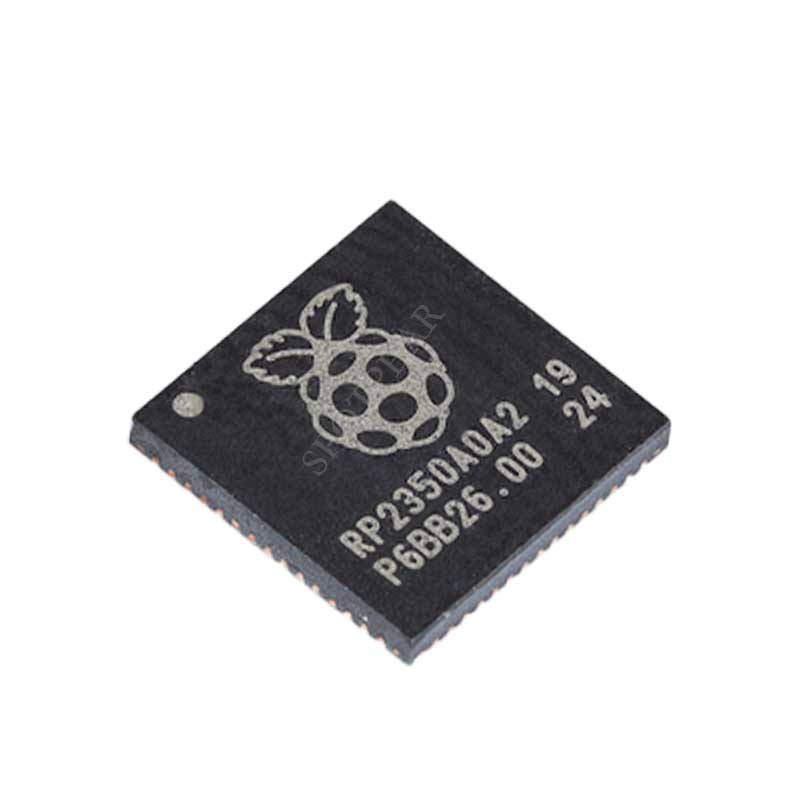

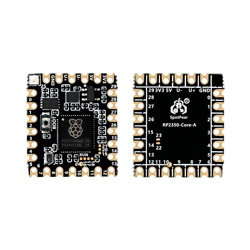

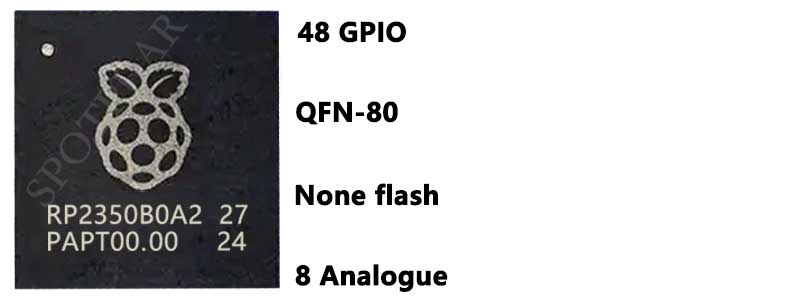

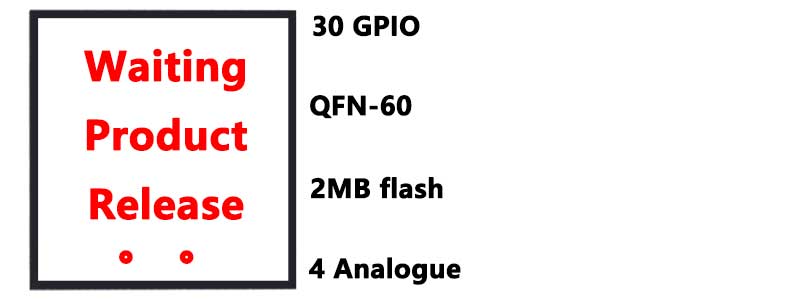

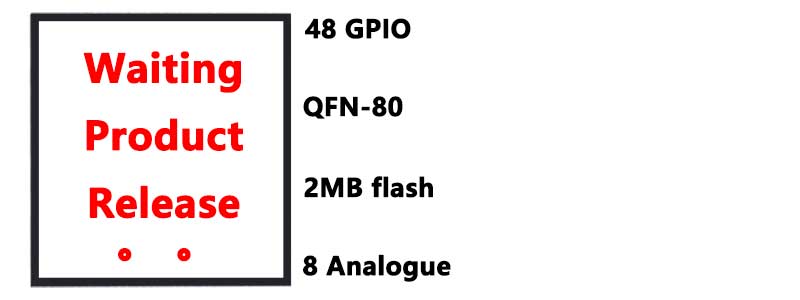

Chip RP2350A / RP2350B / RP2354A / RP2354B For Raspberry Pi Pico 2 ARM Cortex-M33 Hazard3 RISC-V

$5

Brand:Raspberry Pi

SKU:0101633

Date:2024-11-22 13:34

RP2350 is the new high-performance, secure microcontroller from Raspberry Pi. With a higher core clock speed, double the on-chipSRAM, more powerful Arm cores, optional RISC-V cores, new security features, and upgraded interfacing capabilities,RP2350 delivers a significant performance and feature boost over its predecessor,RP2040.

Raspberry Pi Pico 2 RP2350 Recommend

【Manual】

RP2350-RP2350-AB-product-brief.pdf

【Overview】

[] RP2350 is the new high-performance, secure microcontroller from Raspberry Pi. With a higher core clock speed, double the on-chipSRAM, more powerful Arm cores, optional RISC-V cores, new security features, and upgraded interfacing capabilities,RP2350 delivers a significant performance and feature boost over its predecessor,RP2040.

[] RP2350provides a comprehensive security architecture, built around Arm TrustZone for Cortex-M, and incorporating signed boot, 8KB of antifuse OTP for key storage,SHA-256 acceleration, a hardware TRNG,and fast glitch detectors. These features,including the secure boot ROM, are extensively documented and available to all users without restriction: this transparent approach, which contrasts with the "security through obscurity" offered by legacy vendors, allows professional users to integrate RP2350 into products with confidence.

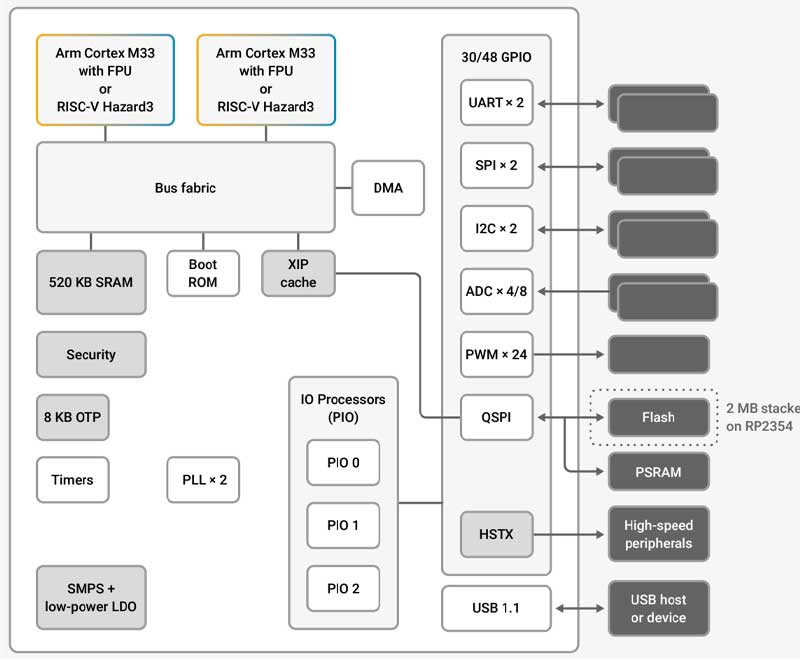

[] The unique dual-core, dual-architecture capability of RP2350 allows users to choose between a pair of industry-standard Arm Cortex-M33 cores, and a pair of open-hardware Hazard3 RISC-V cores. Three high-performance Programmable I/0(PIO) co-processors,with a total of twelve independent state machines, support software-defined interfacing,with little or no CPU overhead.

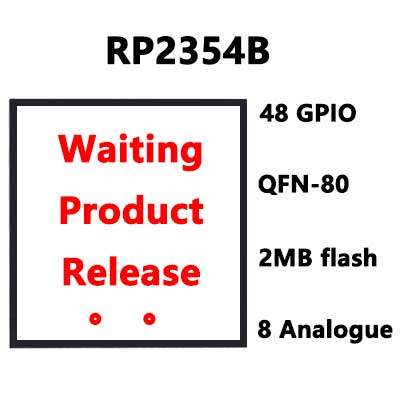

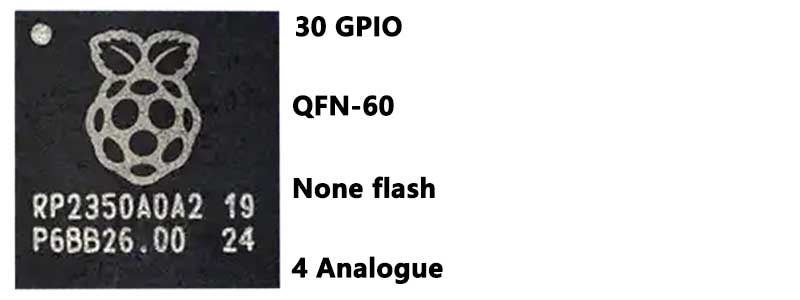

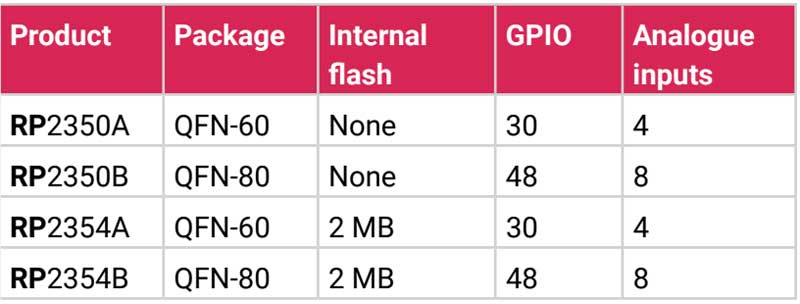

[] RP2350 offers best-in-class performance for a vast range of applications, from cost-optimised embedded computing, to secure applications requiring trusted firmware, to industrial loTdeployments with demanding I/O requirements. It is available in four package variants: with 30 or 48 GPIO pins, and with or without2MB stacked flash memory.

【Key features】

CPU: Dual Arm Cortex-M33 or dual Hazard3RISC-V processors@ 150MHz

Memory: 20KB on-chip SRAM, in ten independent banks

[] Support for up to 16 MB of externalQSPI flash/PSRAM via dedicated QSPI bus; additional 16 MB flash/PSRAM accessible via optional second chip-select

Peripherals: 2xUART

[] 2x SPI controllers

[] 2x12C controllers

[] 24 x PWM channels

[] 4/8x ADC channels

[] 1 x USB 1.1 controller and PHY, with host and device support

[] 12 x PIO state machines

Security features: Optional boot signing, enforced by on-chip mask ROM, with key fingerprint in OTP

[] Protected OTP storage for optional boot decryption key

[] Global bus filtering based on Arm or RISC-V security/privilege levels

[] Peripherals, GPIOs, and DMA channels individually assignable to security domains

[] Hardware mitigations for fault injection attacks

[] Hardware SHA-256 accelerator

Compliance: For a full list of local and regional product approvals, please visit pip.raspberrypi.com

【RP2350 block diagram】

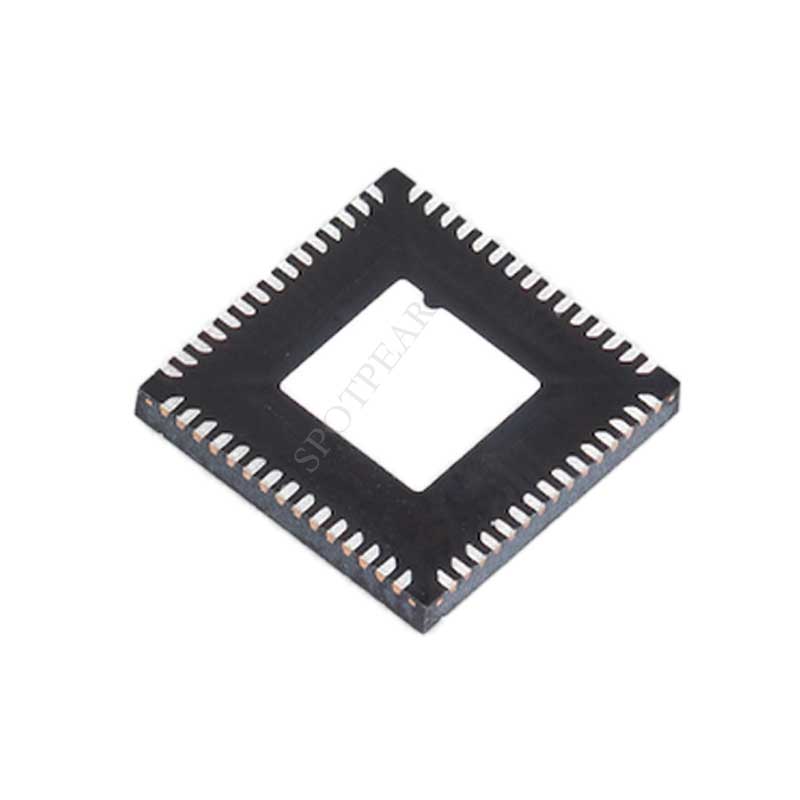

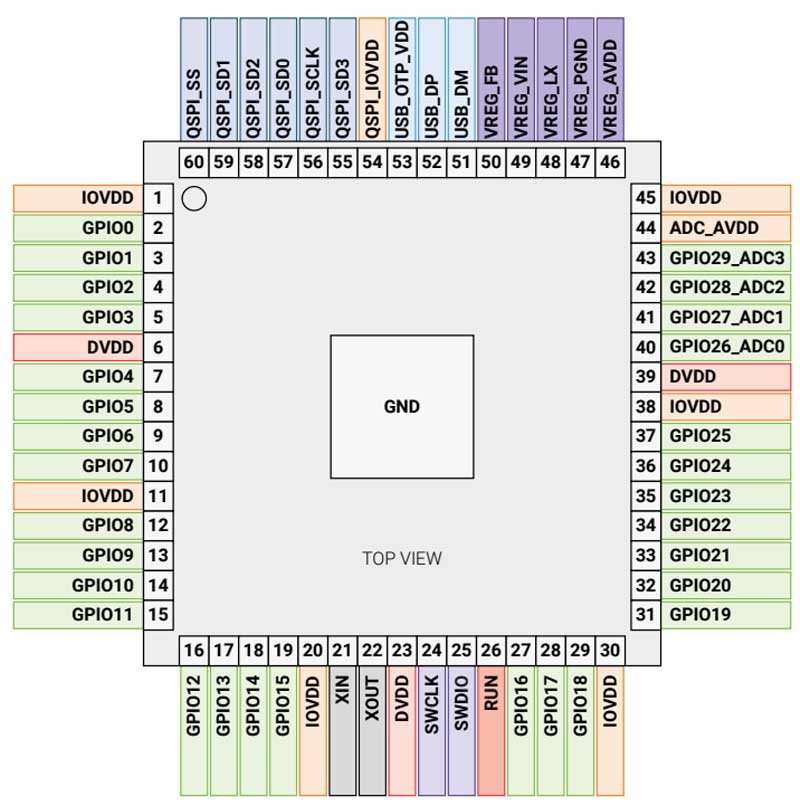

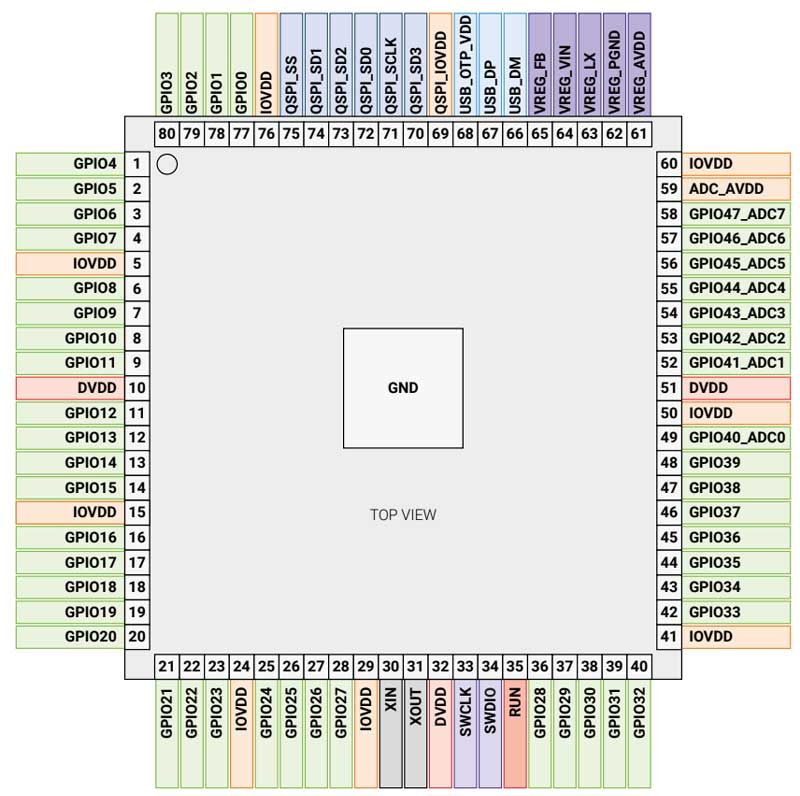

【60QFN pinout】

GPIOX:General-purpose digital input and output

GPIOx/ADCy:General-purpose digital input and output, with analogue-to-digital converter function

QSPIx:Interface to an SPI, Dual-SPI or Quad-SPI flash device, with execute-in-place support

USB_DM and USB_DP:USB controller, supporting full-speed device and full-/low-speed host

XIN and XOUT:Connect a crystal to RP2350's crystal oscillator

RUN:Global asynchronous reset pin; reset when driven low, run when driven high

SWCLK and SWDIO:Access to the internal Serial Wire Debug multi-drop bus; provides debug access to

both processors

GND:Single external ground connection, bonded to a number of internal ground pads on the RP2350 die

QSPI_I0VDD:Provides the IO supply for the chip's QSPI interface

IOVDD:Power supply for digitalGPIOs, nominal voltage 1.8 V to 3.3V

USB_OTP_VDD:Power supply for internal USB full-speed PHY and OTP, nominal voltage 3.3 V

ADC_AVDD:Power supply for analogue-to-digital converter, nominal voltage 3.3 V

VREG_VIN:Power input for the internal core voltage regulator, nominal voltage2.7 V to 5.5V

VREG_FB:Internal core voltage regulator: See datasheet

VREG_LX:Internal core voltage regulator: See datasheet

VREG_PGND:Internal core voltage regulator: See datasheet

VREG_AVDD:Internal core voltage regulator: See datasheet

DVDD:Digital core power supply, nominal voltage 1.1V

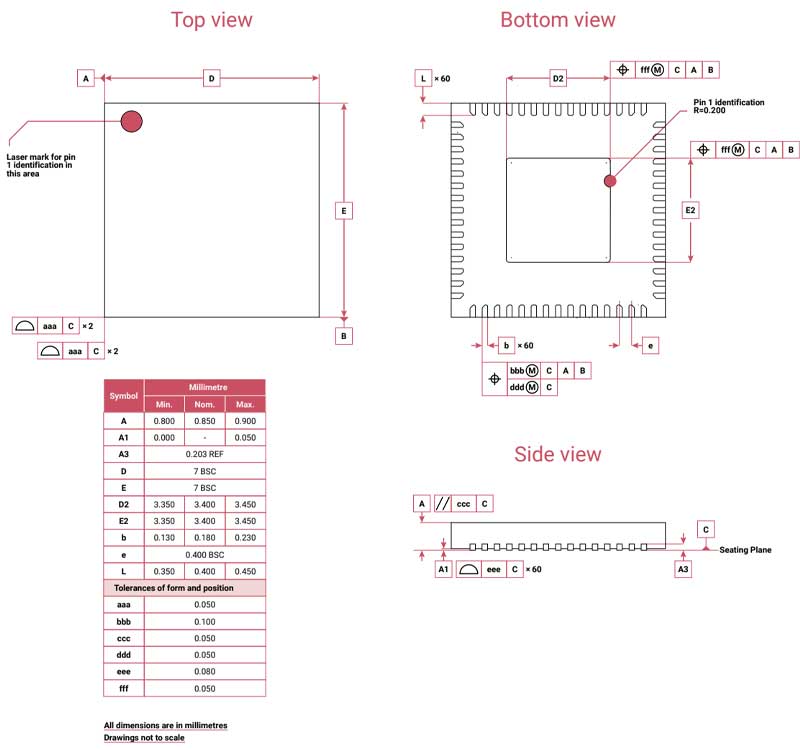

【60QFN physical specification】

【80QFN pinout】

GPIOX:General-purpose digital input and output

GPIOx/ADCy:General-purpose digital input and output, with analogue-to-digital converter function

QSPIx:Interface to an SPI, Dual-SPI or Quad-SPI flash device, with execute-in-place support

USB_DM and USB_DP:USB controller, supporting full-speed device and full-/low-speed host

XIN and XOUT:Connect a crystal to RP2350's crystal oscillator

RUN:Global asynchronous reset pin; reset when driven low, run when driven high

SWCLK and SWDIO:Access to the internal Serial Wire Debug multi-drop bus; provides debug access toboth processors

GND:Single external ground connection, bonded to a number of internal ground pads on the

RP2350 die

QSPI_I0VDD:Provides the IO supply for the chip's QSPI interface

IOVDD:Power supply for digitalGPIOs, nominal voltage 1.8 V to 3.3V

USB_OTP_VDD:Power supply for internal USB full-speed PHY and OTP, nominal voltage 3.3 V

ADC_AVDD:Power supply for analogue-to-digital converter, nominal voltage 3.3 V

VREG_VIN:Power input for the internal core voltage regulator, nominal voltage2.7 V to 5.5V

VREG_FB:Internal core voltage regulator: See datasheet

VREG_LX:Internal core voltage regulator: See datasheet

VREG_PGND:Internal core voltage regulator: See datasheet

VREG_AVDD:Internal core voltage regulator: See datasheet

DVDD:Digital core power supply, nominal voltage 1.1V

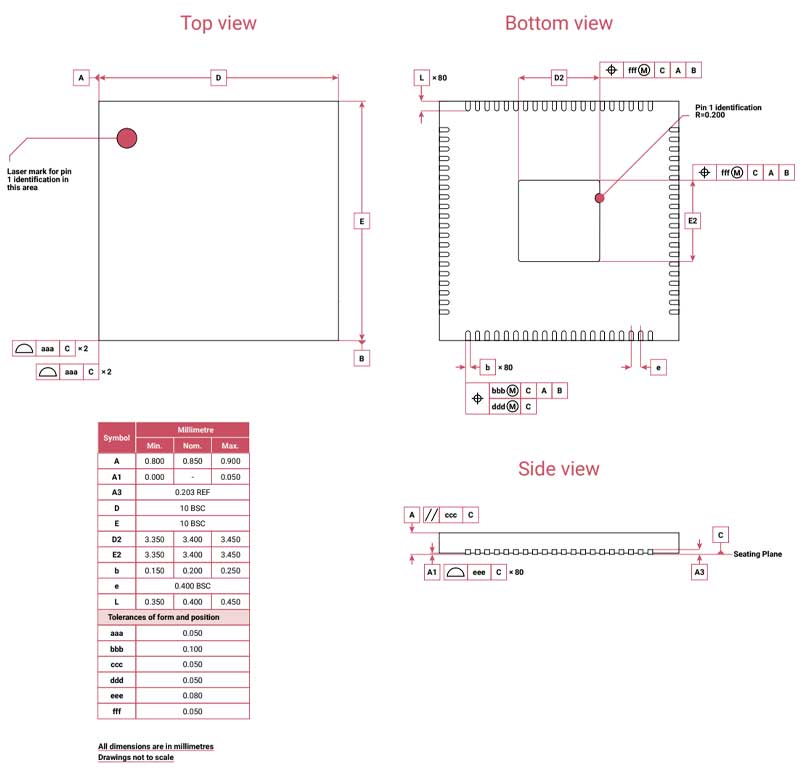

【80QFN physical specification】

TAG:

Allwinner H618

Jetson

Flipper Zero WiFi multiboard NRF24+ESP32

Pi4

Raspberry Pi 5

Raspberry Pi SIM7670G LTE-4G-Cat-1 GNSS USB-HUB

Raspberry Pi Audio

Raspberry Pi 5 Audio hat

Dual-MCU-Board

ADXL355BEZ

XIAO-nRF52840 Sense BLE microphone Sensor Arduino MicroPython SeeedStudio Tiny SuperMini

X1005 Raspberry Pi 5 PCIe M.2 NVMe Dual SSD Pi5 Double 2230 2242 2260 2280

Raspberry Pi 5 Red-White Case

Sipeed SLogic USB Logic Analyzer 80M DAPLink CKLink Debugger Tool UART Module

Raspberry Pi 3.7 inch e-Paper link (G) RYBW 416x240 For Arduino / Jetson Nano / STM32

Luckfox Lume Allwinner T153 Linux Development Board 128MB DDR3 Dual Gigabit Ethernet Ports

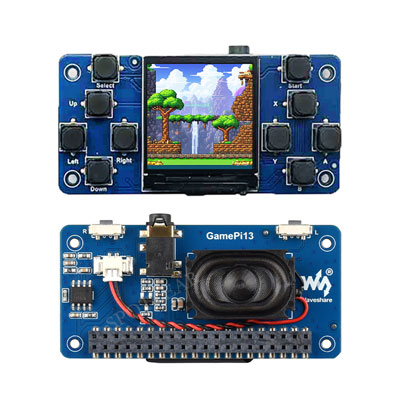

Raspberry Pi 1.3inch LCD

Raspberry Pi 5 PCIe to M.2 NVMe SSD

RPi-POE-A

mobile phone

Forum: